# 50-GHZ INTERCONNECT DESIGN IN STANDARD SILICON TECHNOLOGY

Bendik Kleveland, Thomas H. Lee and S. Simon Wong

Center for Integrated Systems,

Stanford University, Stanford, CA 94305

## ABSTRACT

Coplanar waveguides were fabricated in a process that emulates silicon CMOS technologies with 5 to 10 metal layers. The observed  $S_{21}$  loss of 0.3dB/mm at 50 GHz is among the lowest ever reported with standard Al interconnects on  $\text{Si}/\text{SiO}_2$ . Optimum design parameters were counter-intuitive: in some frequency ranges, the lowest loss was achieved with relatively *narrow* lines over a *low-resistivity* substrate. This was exploited in the design of transmission lines that are fully compatible with a CMOS technology. The process emulation was calibrated with a commercial 4-layer Al/Cu CMOS technology.

## INTRODUCTION

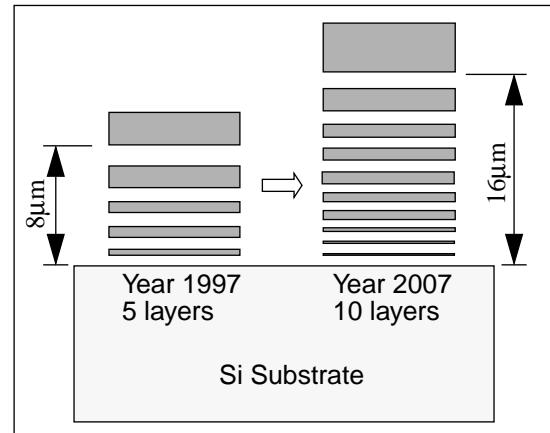

Recently, there has been a great deal of interest to extend digital CMOS into GHz operations and to use standard CMOS for monolithic RF circuits[1]. However, the viability of high-speed interconnects in Si technology has been questioned due to the losses in the Si substrate, the  $\text{SiO}_2$  layer and the metal lines. Various solutions involving a high-resistivity substrate have therefore been proposed[2]-[6], but they are not compatible with standard CMOS technology where a low-resistivity substrate with a thin epi-layer is preferred to reduce latchup and enhance yield[7]. Nevertheless, due to the rapid increase in the number of interconnects, the top level metals will be situated further away from the Si substrate as the technology scales, thus reducing the losses (Fig. 1).

## EXPERIMENT

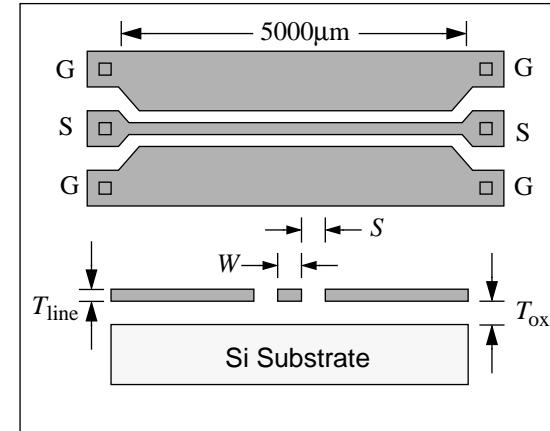

An experiment was conducted to emulate state-of-the-art and future Si CMOS technologies. Low- and high-resistivity (0.5 and  $15\Omega\text{-cm}$ ) Si substrates were used, and LPCVD  $\text{SiO}_2$  (4, 8, 12 and  $16\mu\text{m}$ ) was deposited. Coplanar waveguides (CPW) were fabricated with 2- $\mu\text{m}$  thick Al metallization (Fig. 2).

Fig. 1. Approximate trend of interconnect stack.

Fig. 2. Top and cross-sectional views of a CPW line.

Although future interconnection schemes are likely to incorporate Cu and low- $\epsilon_r$  dielectrics, Al and  $\text{SiO}_2$  were adopted in our study. This technology is readily available and yields conservative results. The layout dimensions of the CPW lines were derived from calculations and 2D simulations[8],[9]. The substrate resistivity and  $T_{\text{ox}}$  dependences were ignored in the calculations for a high-resistivity substrate shown in

Table 1. More accurate modeling[9] confirmed that the impedance of the lines with small coupling to the substrate was adequately predicted by the simple calculations. A wide range of impedances,  $Z_0$ , were implemented.

TABLE 1. CPW Spacing,  $S$ , for various  $W$  and  $Z_0$ .

| WIDTH            | IMPEDANCE ( $Z_0$ ) |                  |                   |

|------------------|---------------------|------------------|-------------------|

|                  | 40 $\Omega$         | 60 $\Omega$      | 90 $\Omega$       |

| 5 $\mu\text{m}$  | 1.25 $\mu\text{m}$  | 5 $\mu\text{m}$  | 20 $\mu\text{m}$  |

| 10 $\mu\text{m}$ | 2.5 $\mu\text{m}$   | 10 $\mu\text{m}$ | 40 $\mu\text{m}$  |

| 20 $\mu\text{m}$ | 5 $\mu\text{m}$     | 20 $\mu\text{m}$ | 80 $\mu\text{m}$  |

| 40 $\mu\text{m}$ | 10 $\mu\text{m}$    | 40 $\mu\text{m}$ | 160 $\mu\text{m}$ |

The  $S$ -parameters were measured with an HP8510C Network Analyzer and Cascade coplanar ground-signal-ground (G-S-G) probes. Reference open pads were used to subtract the pad parasitics, and relatively long lines (5mm) were used in order to obtain accurate measurements.

## RESULTS AND DISCUSSION

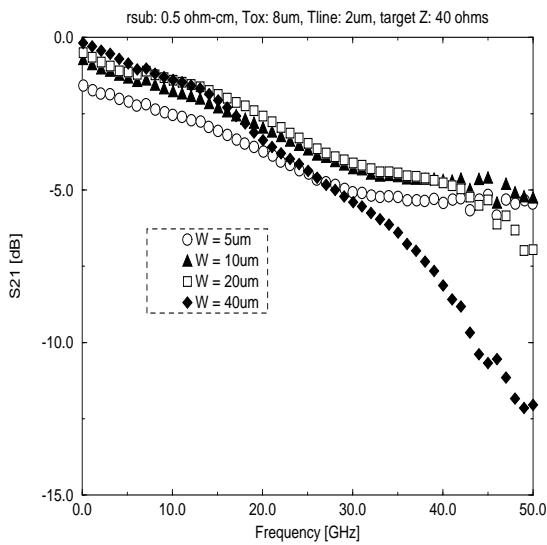

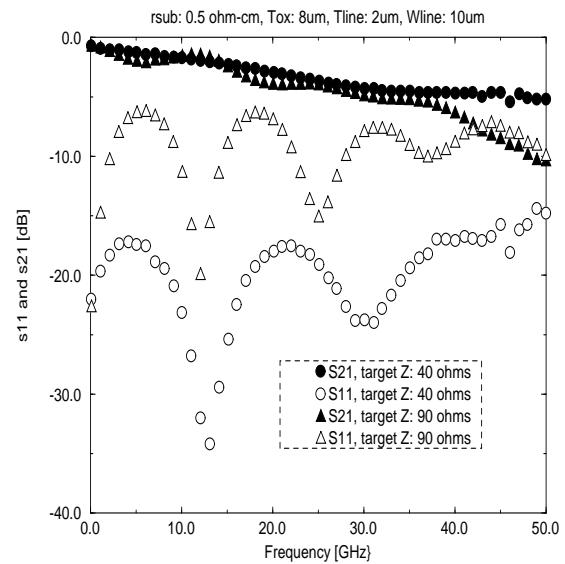

The  $S$ -parameters for a range of line widths with the same impedance ( $40\Omega$ ) revealed some interesting results (Fig. 3). The  $40\mu\text{m}$  wide line has the lowest loss below 10 GHz but the *highest* loss above 30 GHz. The  $S$ -parameters for the  $10\mu\text{m}$  wide line are shown for two different impedances ( $40\Omega$  and  $90\Omega$ )

Fig. 3.  $S_{21}$  for CPW with various widths.

Fig. 4.  $S$ -parameters for CPWs with different target  $Z_0$ .

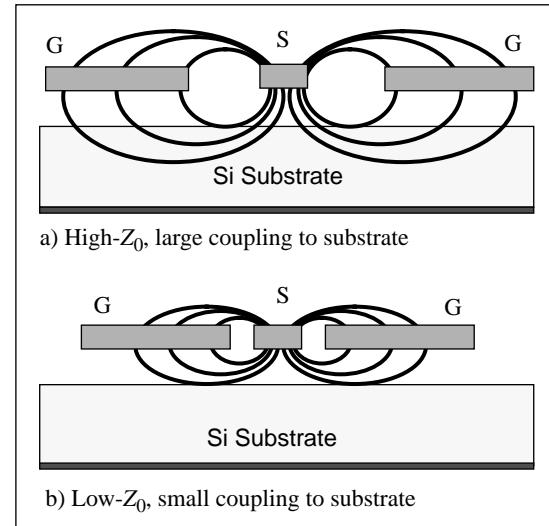

Fig. 5. CPW cross-sections illustrating electric field lines.

in Fig 4. The loss characteristics are similar to those of the wide lines in Fig. 3: the loss increases significantly above 30 GHz due to the large coupling through the substrate. This coupling is illustrated with a sketch of the electric field lines in Fig.5. The coupling through the substrate is more significant when the width or space of the line is larger than  $T_{\text{ox}}$ . Note that at high frequencies, the backside substrate contact is not effective due to the large inductance of the return path: the electric field lines that penetrate into the substrate will terminate on the low-inductance coplanar grounds.

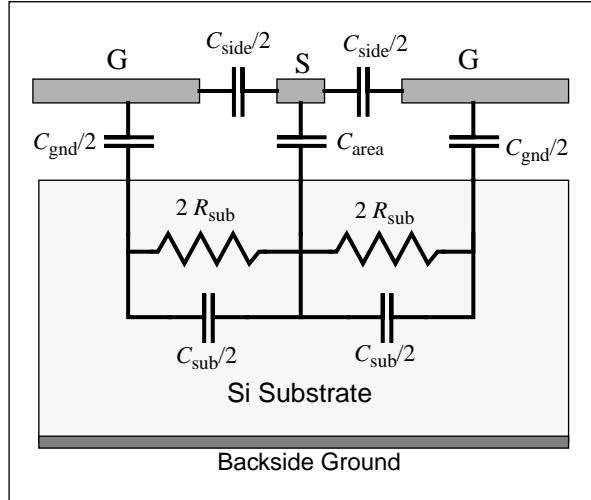

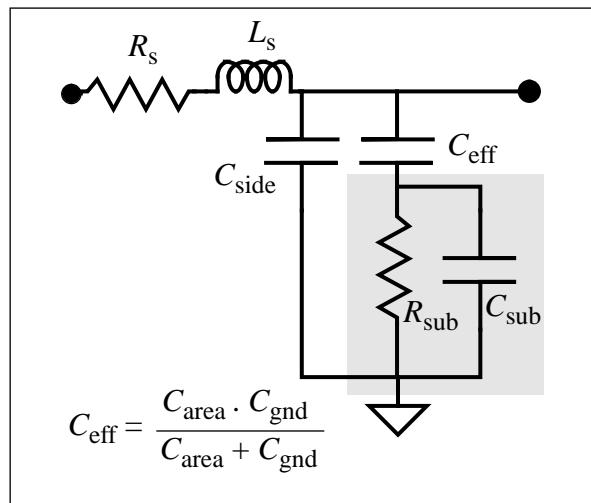

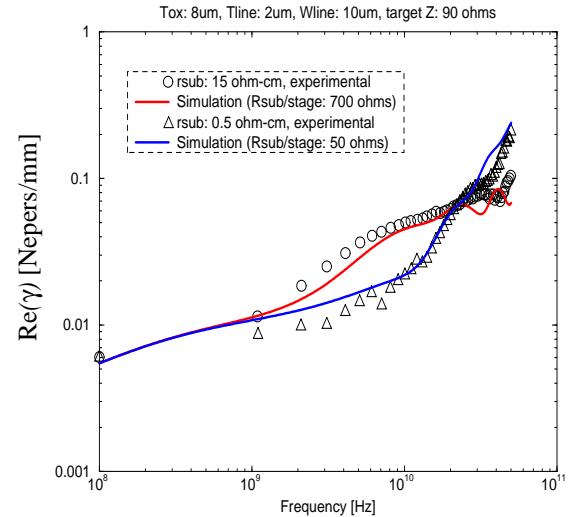

A circuit model was developed to aid the understanding. Assuming small  $\text{SiO}_2$  dielectric losses, the RC components of the CPW line admittance were selected to represent the actual layout (Fig. 6). The frequency-dependent parameters were extracted from the data, and the series combination of  $(C_{\text{sub}} \parallel R_{\text{sub}})$  and  $C_{\text{eff}}$  was fitted to match the admittance[10]-[13] (Fig. 7). A reasonable fit with the experimental data was achieved (Fig. 8). Note that the real part of the propagation constant,  $\text{Re}(\gamma)$ , was *smaller* (i.e., lower loss) for the *low-resistivity* substrate below 20 GHz. This was intriguing since previous work has only strived to obtain lower loss

Fig. 6. Illustration of RC components of CPW line.

Fig. 7. Elements of distributed RLC model of CPW.

Fig. 8. Propagation constant,  $\gamma$ , for CPW lines.

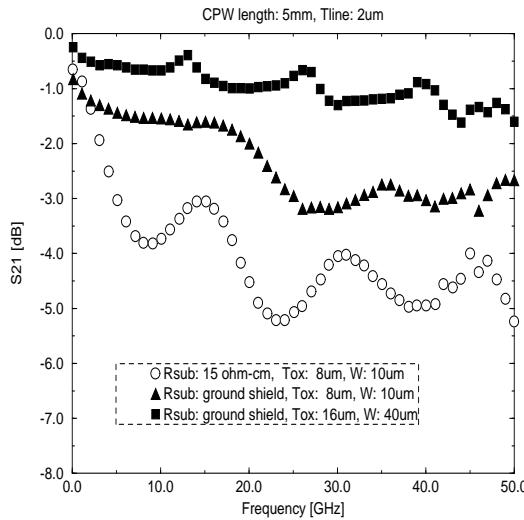

by using *high-resistivity* substrates [3]-[6],[11]-[12]. Furthermore, simulations with the extracted model indicated that the loss could be reduced even further by reducing  $R_{\text{sub}}$ . CMOS epi-wafers typically have a bulk resistivity of  $20\text{m}\Omega\text{-cm}$  which is 25x lower than our ‘*low-resistivity*’ substrates. To examine the extreme of a *low-resistivity* wafer, a  $0.5\mu\text{m}$  thick metal ground plane was inserted beneath the  $\text{SiO}_2$  layer. The  $S_{21}$  loss with the metal ground shield for the 5-metal layer emulation was only  $0.6\text{dB/mm}$  at 50 GHz, and for a future 10-metal-layer technology,  $S_{21}$  was as low as  $0.3\text{dB/mm}$  (Fig. 9). Due to the reduced coupling to the substrate/shield, a wider line could be used. This also supports the assumption of small  $\text{SiO}_2$  dielectric losses - contrary to other observations[5].

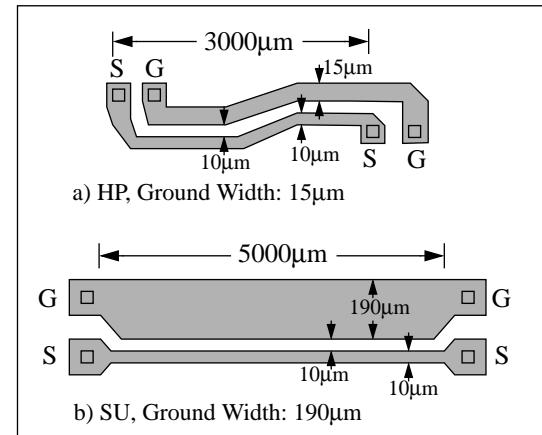

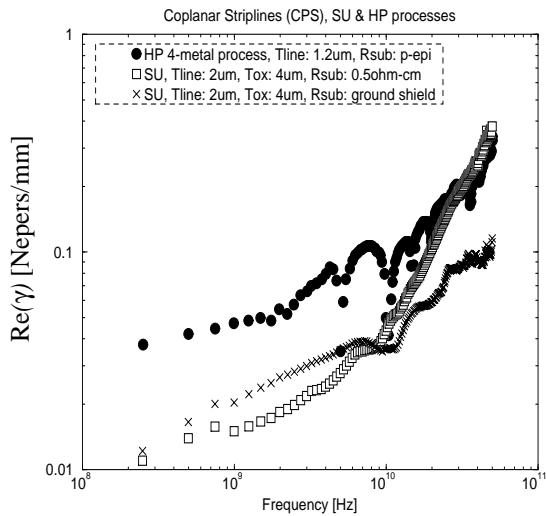

The emulation of the advanced processes was verified with a comparison to a 4-metal-layer industry CMOS process from Hewlett-Packard (HP). Due to area constraints, a shorter coplanar stripline (CPS) was used (Fig. 10). Furthermore, the ground line was also narrower than the structures fabricated at Stanford University (SU). Since the ground return current tends to crowd near the signal line at high frequencies, the width of the ground line should not affect the comparison significantly. The distance to M4 in the HP process is about  $4.4\mu\text{m}$ , and the SU wafers with  $T_{\text{ox}} = 4\mu\text{m}$  yield the best match (Fig. 11). The higher loss ( $\sim 3x$ ) in the HP process is primarily attributed to the relatively thin metal line ( $1.2\mu\text{m}$  Al/Cu vs.  $2\mu\text{m}$  100% Al). The

Fig. 9.  $S_{21}$  for various CPW lines.

impedances are similar:  $65\Omega$  at 1 GHz. Note that the trend of loss vs. frequency resembles more closely the SU with ground shield, whereas the loss for the SU with  $0.5\Omega\text{-cm}$  substrate has a steeper increase vs. frequency.

## CONCLUSION

Two techniques of achieving low-loss coplanar waveguides were demonstrated: 1) reduce line widths and spacing to avoid substrate coupling and 2) use low-resistivity substrate or metal/poly/diffusion to provide a low resistance for the lateral ground connection. The loss is expected to be further reduced with the increasing number of interconnects and thicker, lower-resistivity top-level metallization in future technologies.

## ACKNOWLEDGMENTS

This work was funded by Silicon Graphics Inc. and National Science Foundation (MIP-9313701). We gratefully acknowledge fabrication support and valuable discussions with Carlos Diaz and Melody Ma of ULSI research lab, HP Laboratories. We also thank Liam Madden, C. Patrick Yue, Alvin L. S. Loke and Vonny F. Lee for very useful discussions.

## REFERENCES

- [1] A.R. Shahani et al., "12mW wide dynamic range CMOS front-end for a portable GPS receiver," ISSCC-97, p. 368.

- [2] M.T. Bohr, "Interconnect scaling - the real limiter to high performance ULSI," IEDM 95, p. 242.

- [3] B. K. Kim et al., "Monolithic planar RF inductor and waveguide structures on silicon with performance comparable to those in GaAs MMIC," IEDM 95, p. 717.

Fig. 10. Top view of the CPS lines.

Fig. 11. Propagation constant,  $\gamma$ , for CPS lines.

- [4] J. Chuang et al., "Air-gap transmission lines for OEICs and MMIC using glass substrates," 97 IEEE MTT-s Digest, TU4B-1, p. 265.

- [5] H. Sakai et al., "A millimeter-wave flip-chip IC using micro bump bonding technology," ISSCC-96, p. 408.

- [6] C. Reinfelder et al., "26 GHz coplanar SiGe MMICs," 96 MTT-s Digest, TU4A-6, p. 273.

- [7] L. O. Borland et al., "Improved CMOS device performance through Si epitaxial intrinsic gettering techniques," 84 Conf. Sol. State Dev. p. 487.

- [8] G. Ghione et al., "Analytical formulas for coplanar lines in hybrid and monolithic MICs," El. Lett., 20 (4), p. 179.

- [9] Maxwell 2D simulator from Ansoft Corporation, version 1.8.22, 1997

- [10] Y.-C. Shih, "Broadband characterization of conductor-backed coplanar waveguide on-wafer meas. techniques," Microwave Journal, Apr 91, p. 95.

- [11] W. R. Eisenstadt et al., "S-parameter based IC interconnect transmission line characterization," IEEE Trans. Comp. Hybrid 15 (4) -92, p. 483.

- [12] Y. Eo et al., "High-Speed VLSI interconnect modeling based on S-parameter measurements," IEEE Trans. Comp. Hybrid 16 (5) -93, p. 555.

- [13] J.-S. Ko et al., "Simple modeling of coplanar waveguide on thick dielectric over lossy substrate," IEEE Trans. El. Dev. 44 (5) -97, p. 856.